Fast TSC calibration failed

The Time Stamp Counter (TSC) is a 64-bit register present on all x86 processors since the Pentium. It counts the number of cycles since reset.

The time stamp counter has, until recently, been an excellent high-resolution, low-overhead way of getting CPU timing information. With the advent of multi-core/hyper-threaded CPUs, systems with multiple CPUs, and hibernating operating systems, the TSC cannot be relied on to provide accurate results -unless great care is taken to correct the possible flaws: Rate of tick and whether all cores (processors) have identical values in their time-keeping registers-. There is no promise that the timestamp counters of multiple CPUs on a single motherboard will be synchronized. In such cases, programmers can only get reliable results by locking their code to a single CPU. Even then, the CPU speed may change due to power-saving measures taken by the OS or BIOS, or the system may be hibernated and later resumed (resetting the time stamp counter). In those latter cases, to stay relevant, the counter must be recalibrated periodically (according to the time resolution the application requires).

If you noticed that there was an error on your install during bootup that said something like:

tsc: Fast TSC calibration failed

The error about Fast TSC shown above can be ignored… Because it is just letting you know that it failed on its first attempt. You can verify that it succeeds by looking in /var/log/messages:

~$ su -

~# cat /var/log/messages | grep TSC

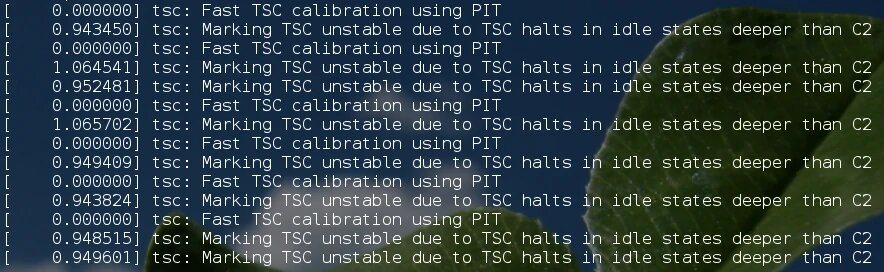

The output here should be filled with successful TSC checks… Or not. For example:

tsc: Fast TSC calibration using PIT

tsc: Marking TSC unstable due to TSC halts in idle states deeper than C2

If I do

~# cat /sys/devices/system/clocksource/clocksource0/available_clocksource

This will return

hpet acpi_pm

If I do

~# cat /sys/devices/system/clocksource/clocksource0/current_clocksource

This will return

hpet

It is a correct and most optimal fallback and should not be overidden. Honestly, you can ignore this error.

You can read the article from Ravi Murty (Intel) : Eliminate the dreaded “clocksource is unstable” message: Switch to TSC for a stable clock source option for Linux when using an Intel® Xeon Phi™ Coprocessor .